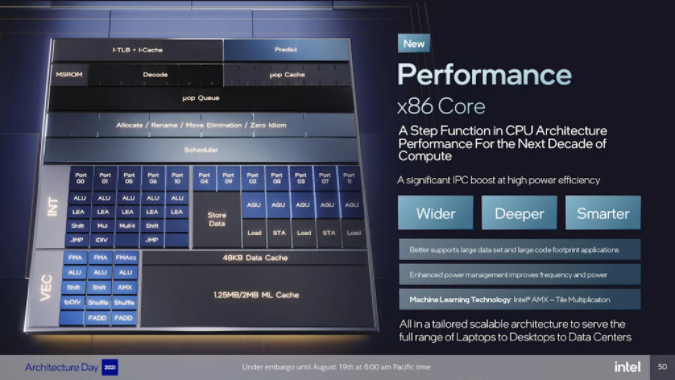

Alder Lake 的 P-Core︰ Golden Cove 大核心

Alder Lake 的 P-Core 代號為 Golden Cove 的大核心,它的設計是基於 Tiger Lake 的 Willow Core 核心作出大規模的改良,目的是擁有更寬的前端指令解碼能力、更深的亂序執行能力、更大的緩存能力、更聰明的調度並加快預測分支的進行和降低分支失敗率,以達至提升運算速度和進一步降低延遲,以突破單線程應用程序的性能局限,較上一代帶來 19% IPC 性能提升,Intel 更表示 Golden Cove 是過去 10 年來最大的微架構升級。

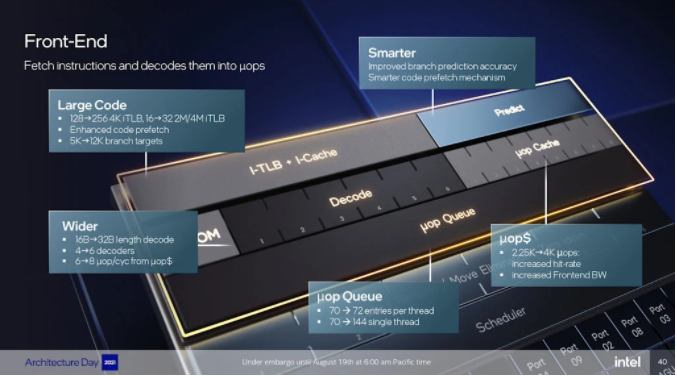

經改良的 Front End 引擎

Golden Cove 的 Front End 引擎最大的改良就是將 x86 Decoder 由 4-Wide 提升至 6-Wide,即令每個週期可處理 x86 指令由 4 個提升至 6 個,同時每個週期可以提取的 μOps 亦由 6 個提升至 8 個,解碼長度從 16 Bytes 倍升至 32 Bytes,為 Front-End 引擎提供更高的 x86 指令吞吐量。

此外, Golden Cove 另一個改良是擁有更大的 Branch Predictor Bandwidth,4K iTLB 由 128 提升至 256 Entries,2M/4M iTLB 則由 16 提升至 32 Entries,L2 Branch Targets Buffer (BTB) 則由 5K 增加至 12K Entries,這更大的 Branch Bandwidth 有助更快的分支錯誤回復,減少預測迼成的預測泡沫,能加快預測分支的進行並降低分支失敗率。

為提升 Micro-Tags 的效率,μOps Cache 緩存由 2.25K 條提升到 4K,譠更多解碼後的 μOps 指令可被暫存,當遇上相同的 x86 指令時,不用再 Decoder 單元進行解碼,直接由 μOps Cache 緩存單元內提取 μOps 指令,為 Frond-End 引擎提供更大的指令解碼吞吐量。

此外 μOps Queue 隊列深度也由上代 Willow Cove 的 70 Entries per thread,改善到今代 SMT 雙線程下略增至72 Entries per thread,在單線程下可以將閒置的 μOps Queue 完全利用,達至 144 Entries per thread,這是更聰明地 Prefectch 機制實現更高的 Branch Prediction 命中率。

更寬的 Out of Order 引擎

Golden Cove 將 Out of Order 引擎的 Allocation 由 5-Wide 增至 6-Wide,同時將 Re-order Buffer 由 352 增至 512 Entries,Back-end 則由上代 Willow Cove 的 10 個 Execution Ports 增加至 12 個,目的是要進一步降低運算延遲,並且進一步提高指令層面的平行運算能力,而這一代的 IPC 效能提升,很大程度是來自 Re-order Buffer 的增加。