Back-End 與記憶體子系統

不過在 Back-End 執行端口設計方面,Golden Cove 的執行端口仍然以 Unified Reservation Station 設計,沒有像 AMD Zen 3 中將 INT 整數及 FP 淨點運算群獨立分開,雖然共用流水線及執行端口能減少電晶體的數量,但 SMT 同步多線程運算性能會有所降低,所以 Intel 在後端設計中,未來還有改良的空間。

Back-End 方面,Golden Cove 的 Unified Reservation Station 增加了 Port 10 端口,令執行 Integer Execution 整數運算的端口由 4 個增至 5 個,Port 10 端口具有 ALU 運算和 LEA 儲存指令,這令 Golden Cove 成為所有 x86 微架構中原始 ALU 吞吐量最高的核心。而 Golden Cove 的 5 個 LEA 單元都是可以在單一週期內完成,可應用在加法、減法和固定數字的快速乘法,相較 Tiger Lake 的 Willow Cove 部份指令要 2 個週期才能完成,性能明顯大幅提升。

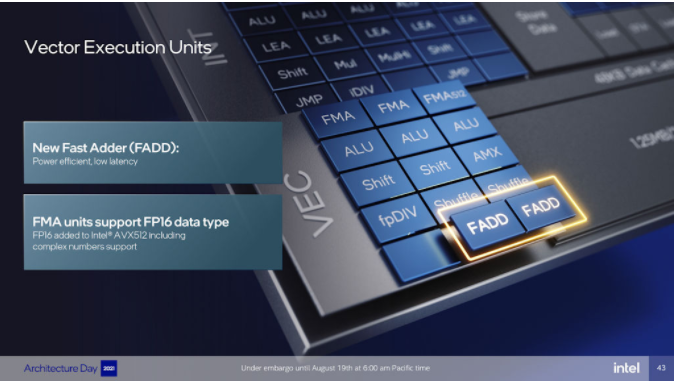

在浮點運算方面,Golden Cove 在 Port 01 與 Port 05 的端口增加了 FADD 單元,處理 FADD 指令時相較使用 FMA 單元性能更高且延遲更低,同時針對 FMA 單元亦作出了強化,新增 FP16 指令支援令低精度運算加速,不過這是 AVX-512 指令集的功能,如未能使用 AVX-512 的情況下,是不會使用到它的。

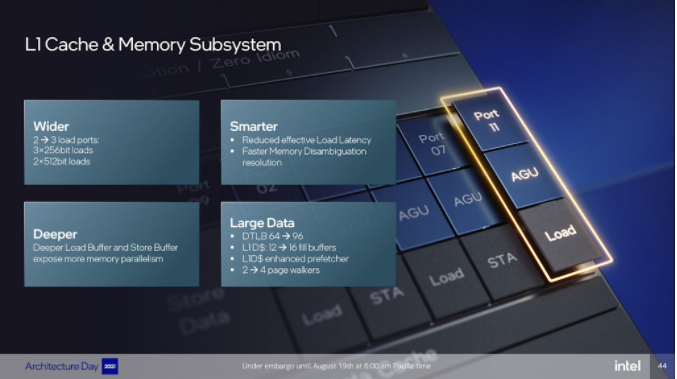

Load / Store 單元方面,Golden Cove 新增了 Port 11 並增加了 1 個 256bit 的 Load 加載單元,將每個週期的加載數量由上代 Willow Cove 的 2 個 512bit 資料,提升至 3 個 256bit 或 2 個 512bit 資料,追數量上追上了 AMD Zen 3 微架構。

在 L1 Data TLB 由 64 增至 96 Entries,L1 Data Cache 由 12 個增至 16 個 Fill Buffers,並且改良了 L1 Data Cache 強取器的性能,由上代的 2 頁增至 4 頁面,讓 TLB 未命中時可以速查找更多頁面的資料。更寬的 Cache Subsystem 結構與更佳的資料預取,盡量填充 Execute Engine 減低閒置及延遲。

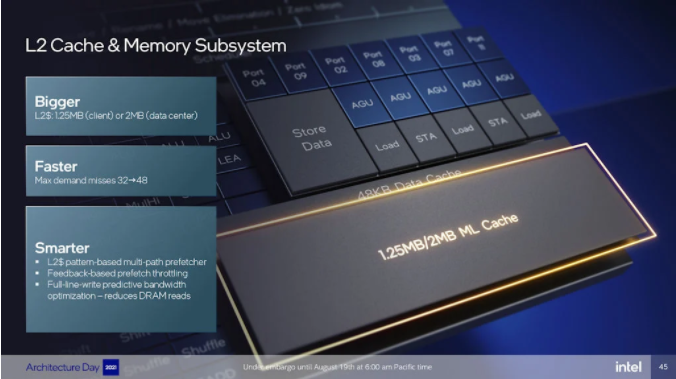

而在 L2 Cache 方面,Golden Cove 的 L2 Cache 則沿用了 Willow Cove 的設計,每個核心具備 1.25MB L2 Cache、非包含式設計。增加了平行數據訪問未完成請求數量由 32 條增至 48 條,同時 L2 Cache 的預取單元亦作出了改良,避免要完全覆寫相同的資燉至 Cache Line 之中,從而降低 Prefetch Throtting 問題使緩存性能有所提升。