改良的 Cache Subsystem 架構

為進一步提升處理器吞吐量,AMD Zen 3 微架構針對 Cache Subsystem 作出了多項改良,更高的 Load/Store Bandwidth,更大的使用彈性,改良記憶體子系統的依存偵測,更大的 Cache System 結構與更佳的資料預取等,盡量填充 Execution Engine 減低閒置及延遲。

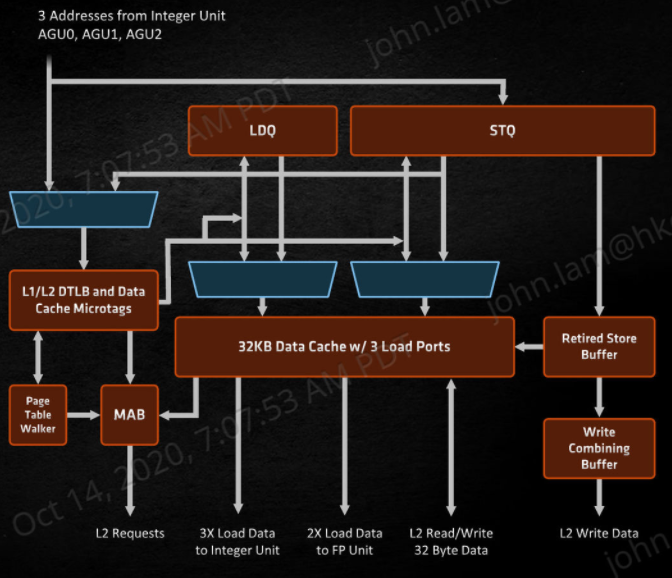

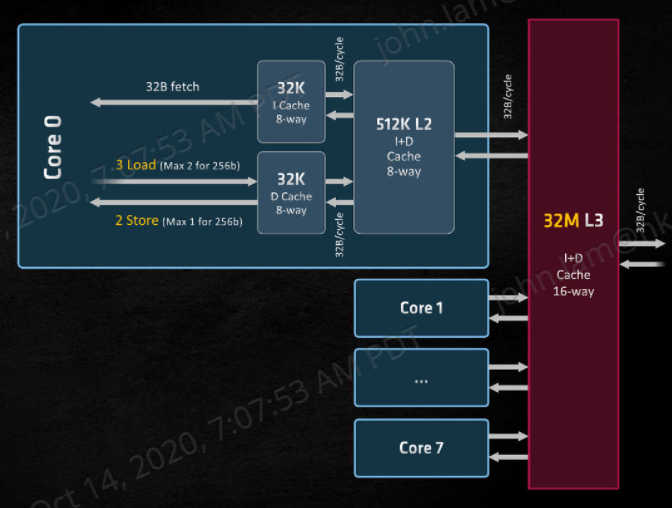

AMD Zen 3 微架構中的 L1 Cache 容量保持 32 KB,同樣為 8-Way 關聯性,Load Queue 單元保持 72 個 Out of order 無序載入隊列,最高可提供 3 Load per Cycle (INT) 及 2 Load per Cycle (FP),Store Queue 單元則設有 64 個儲存隊列,比上代的 48 個增加不少,每個週期最高可處理 2 Store per Cycle,緩存讀寫吞吐量提升了一倍。

AMD Zen 3 微架構中還提供了更快的短字串資料拷貝功能,改良了 L1 Cache 頁面之間的預取延遲,同時降低了 Store to Load 預測分支單元的載入延遲,加上更快的 512KB、8-Way L2 Cache,同時與 L1 Instruction Cache 之間提升至雙向 32 Bytes per Cache,能大幅降低 Preferch Throtting 問題令緩存性能有所提升。

統一的 L3 Cache 與 CCX 設計

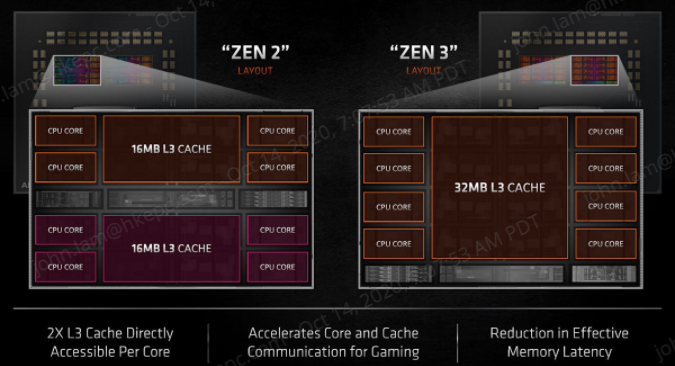

AMD Zen 3 微架構中的一個重大改動,就是 SoC 架構設計,跟上代 Zen 2 (Matisse) 微架構的 8 核心 CCD 晶片相比,Zen 2 的 CCD 由 2 個 CCX 模組構成,每個 CCX 模組擁有 4 個核心並共享 16MB L3 Cache,而 Zen 3 (Vermeer) 則改為單一 CCX 模組設計,CCX 模組具備 8 核心共享 32 MB L3 Cache,這個改動,可以消除不同 CCX 之間 Core to Core 及 Core to Cache 的讀取延誤。

為了改為單一 CCX 模組設計,AMD Zen 3 加入了全新的 Ring Bus 架構,讓 Core to Core 及 Core to Cache 可以直接透過 Ring Bus 溝通,這設計跟 Intel Core 十分相似,雖然 Zen 2 和 Zen 3 同樣都有 32MB L3 Cache,但在效能方面也明顯提升了不少。據 AMD 白皮書指出,AMD 針對 SoC 架構的改良,在 1080p 遊戲性能上,比上一代提升了 26%,如果執行針對 CPU 運算敏感的遊戲,如 League of Legends、Counter-Strike、Global Offensive 及 PUBG 等,遊戲性能甚至會提升 40-50%。